目录

挖坑快排:

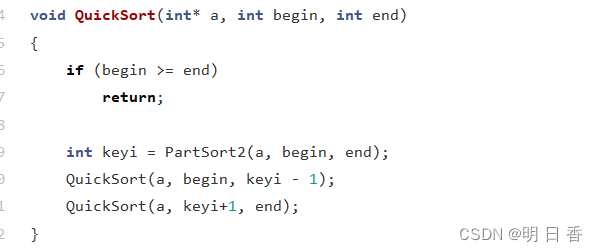

代码实现:

代码分析:

前后指针快排:

编辑动画分析:

代码分析:

代码演示:

快排的优化:三数取一

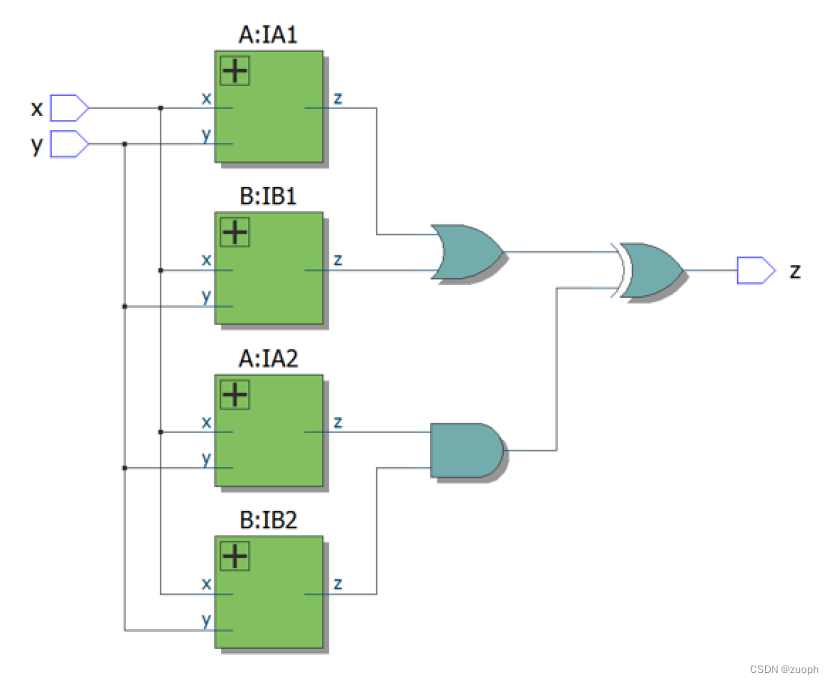

挖坑快排:

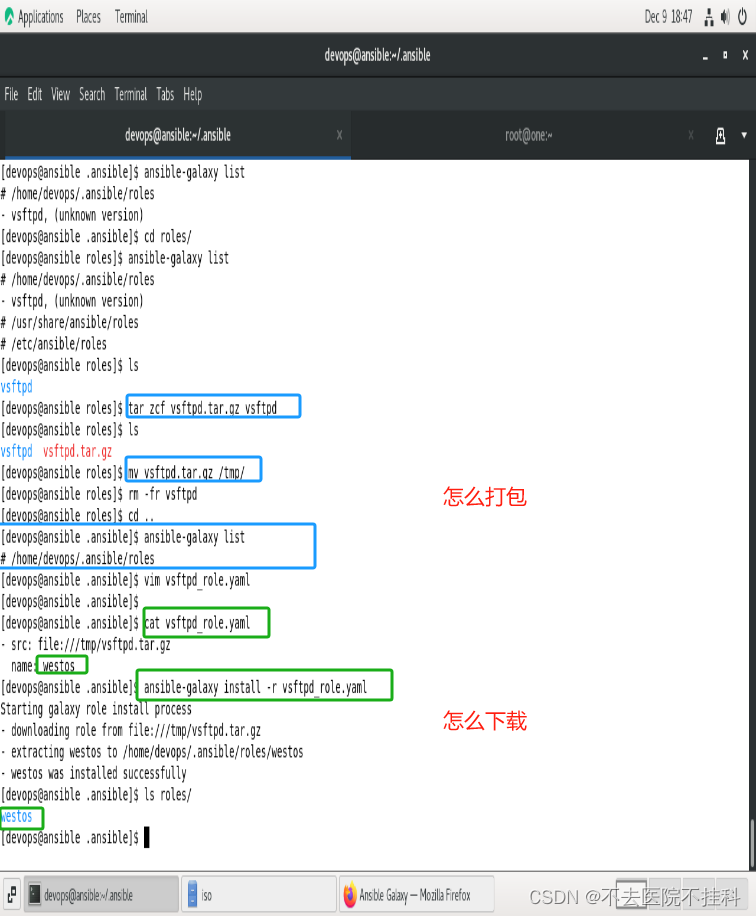

挖坑法,顾名思义,先把key这个标准值取出,随后之前key所在的位置就成为了坑位,然后和hoare的方法一样进行左右进行遍历

只不过不同的是当右边遇到比key小的数时,会把这个数取出,然后放入坑位所在的位置,随后被取出的那个数的所在位置就是新的坑位了

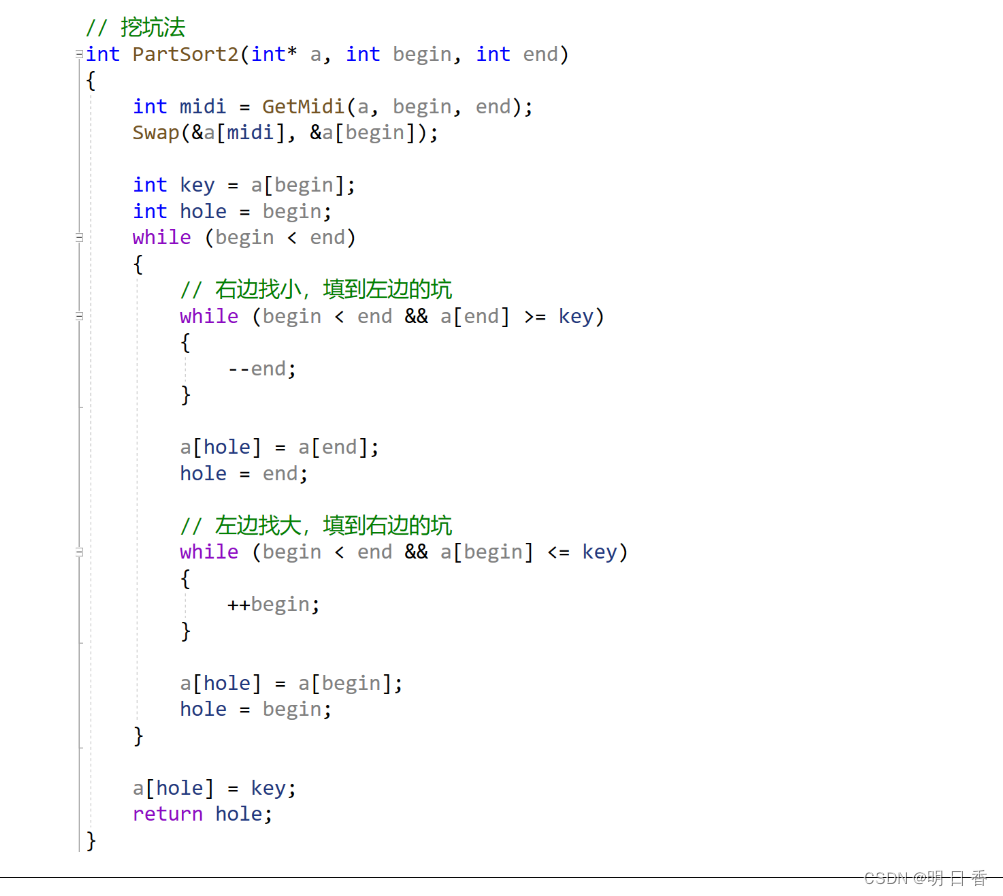

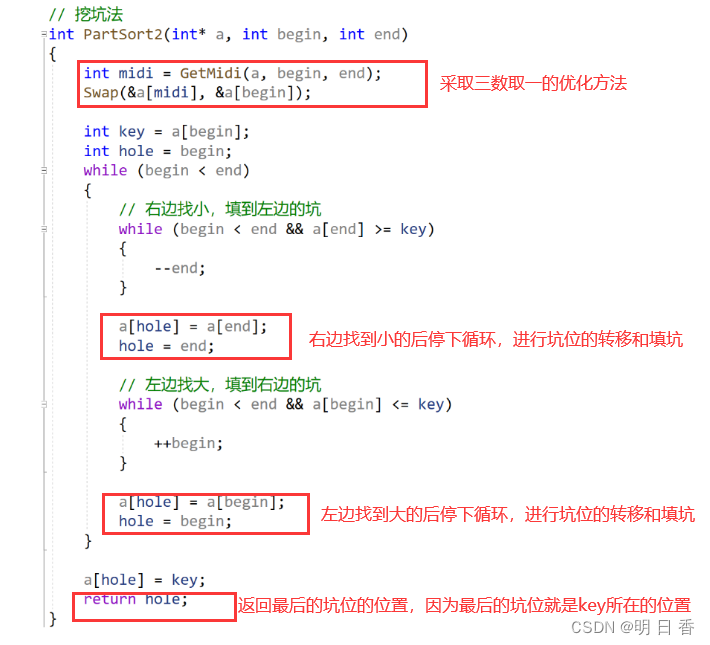

代码实现:

代码分析:

当然,挖坑快排和快排一样,需要使用递归,而这里将递归变成了一个外部的调用函数,由挖坑排序返回最后的key值,再外部调用函数中进行分割序列然后递归调用。

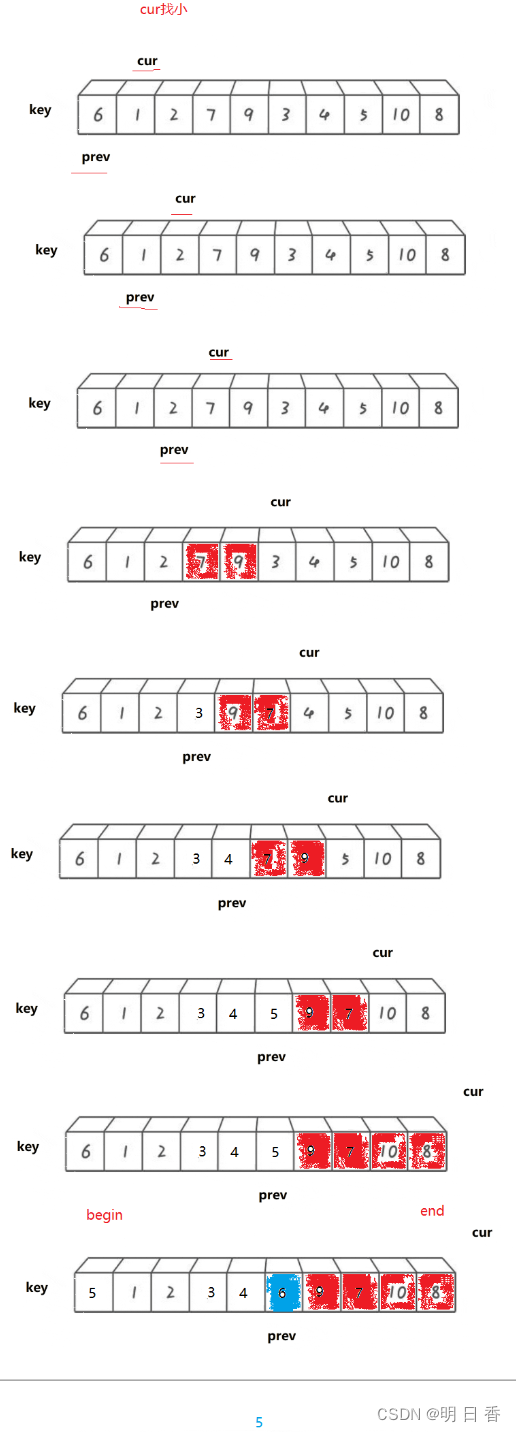

前后指针快排:

前后指针的用法略微的巧妙和复杂,先设置两个指针,一个叫cur,一个叫prev

- cur指针是查看是否有比key值小的元素,如果有遇见比key小的元素,则prev移动,随后将prev所处位置的元素和cur所处位置的元素交换,交换完成后cur往前移动。

- 而若cur指针遇见比key值大的元素,则进往前移动。

- 最后cur越界后,将prev所处的位置元素和key所处位置的元素进行交换。

动画分析:

动画分析:

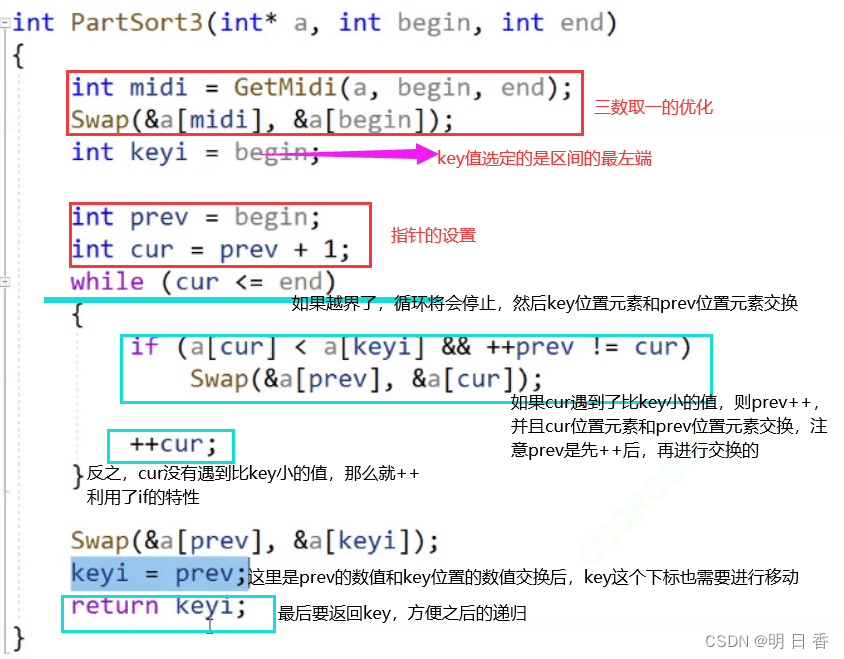

代码分析:

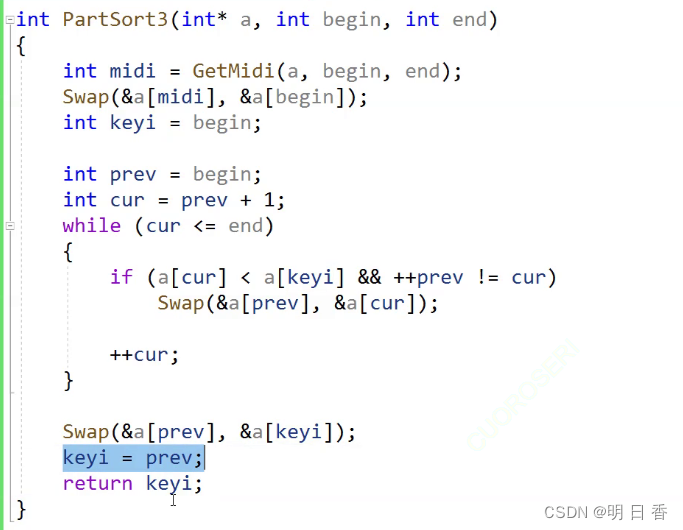

代码演示:

快排的优化:三数取一

快排的优化是针对与key取值的优化,也就说优化key这个数值的大小,使得这个数值本身就是一个不大不小的数值,以此来减少排序的次数,从而达到优化作用

三数取一,最后返回的是下标,我们需要再一组序列的前端、后端以及中间位置的元素中找到一个不大不小的元素作为我们的中间值,随后用中间值和最左位置进行交换,从而将key值进行优化 (默认的key值都是最左端的数)